# NY5QxxxA Series (OTP)

# Single-Chip 4-bit MCU & 4-ch Speech/Midi

Version 1.3

May 27, 2022

NYQUEST TECHNOLOGY CO. reserves the right to change this document without prior notice. Information provided by NYQUEST is believed to be accurate and reliable. However, NYQUEST makes no warranty for any errors which may appear in this document. Contact NYQUEST to obtain the latest version of device specifications before placing your orders. No responsibility is assumed by NYQUEST for any infringement of patent or other rights of third parties which may result from its use. In addition, NYQUEST products are not authorized for use as critical components in life support devices/systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of NYQUEST.

# **Revision History**

| Version | Date       | Description                                                                                                      | Modified Page     |

|---------|------------|------------------------------------------------------------------------------------------------------------------|-------------------|

| 1.0     | 2021/07/29 | Formal release.                                                                                                  | -                 |

| 1.1     | 2021/11/30 | <ol> <li>Modify ROM Mapping.</li> <li>Modify DC Characteristics.</li> <li>Modify Application Circuit.</li> </ol> | 8<br>15<br>17     |

| 1.2     | 2022/02/15 | 1. Add SOP8, SOP16 package                                                                                       | 23                |

| 1.3     | 2022/05/27 | <ol> <li>Add NY5Q026A, NY5Q046A, NY5Q080A, and NY5Q160A</li> <li>Note of Application Circuit</li> </ol>          | 3, 6, 19-22<br>17 |

# Nyquest

#### 1. 概述

NY5Q 系列產品爲多功能單晶片CMOS語音合成4位元微控制器,是九齊科技爲了支援新 NY5 (NY5+) 系列所專 門開發的崁入式EPROM架構的OTP IC (One Time Programmable)。提供4通道的語音/Midi合成功能,語音合成 方式採用先進的高音質ADPCM演算法,最高採樣率可達CD音質44.1KHz,且硬體有音量控制。提供兩種聲音輸 出方式可供選擇,一種PWM輸出和一種DAC輸出。PWM 模式內建增強降低底噪輸出。MCU 使用RISC精簡指令 集架構,共有43條指令,除了少數指令需要2~3個時序,大多數指令都是1個時序即可完成,可以很方便的以程式 控制來完成不同的應用。利用精準的+/- 0.5%內阻震盪,客戶可以不需外加震盪電阻。提供待機模式(Halt mode),可大幅度的節省功耗;另外還提供慢速模式(Slow mode),可以降低功耗。

# 2. 功能

- 寬廣的工作電壓: 2.0V~5.5V。

- 4-bit RISC 精簡指令集架構的微控制器,共有43條指令。

- 共有10個OTP母體,最大母體的ROM容量為832Kx10-bit,程式和資料共用同一塊ROM。ROM容量,秒數和 I/O腳數如下:

| ІС Туре  | Time* (sec) | ROM (bits) | RAM (bits) | I/O | PWM-IO | Channel | DAC |

|----------|-------------|------------|------------|-----|--------|---------|-----|

| NY5Q020A | 18.3        | 48K x 10   | 248 x 4    | 8   | -      | 4       | Y   |

| NY5Q026A | 25          | 64K x 10   | 248 x 4    | 4   | -      | 4       | Y   |

| NY5Q040A | 38.3        | 96K x 10   | 248 x 4    | 8   | -      | 4       | Y   |

| NY5Q046A | 45          | 112K x 10  | 248 x 4    | 12  | 8      | 4       | Y   |

| NY5Q060A | 58.3        | 144K x 10  | 248 x 4    | 16  | 8      | 4       | Y   |

| NY5Q080A | 78.3        | 192K x 10  | 248 x 4    | 12  | 8      | 4       | Y   |

| NY5Q092A | 91.6        | 224K x10   | 248 x 4    | 16  | 8      | 4       | Y   |

| NY5Q160A | 158.3       | 384K x 10  | 248 x 4    | 12  | 8      | 4       | Y   |

| NY5Q172A | 171.6       | 416K x 10  | 248 x 4    | 16  | 8      | 4       | Y   |

| NY5Q342A | 345         | 832K x 10  | 248 x 4    | 20  | 8      | 4       | Y   |

\* 聲音秒數以 6 KHz 4-bit ADPCM 計算.

- 248x4-bit RAM,支援間接定址模式。

- 1MHz 或 2MHz指令頻率。(使用兩通道以上需選擇 2MHz)

- 提供慢速模式(Slow mode),可降低功耗。(注意:由於慢速模式的時間誤差較大,不建議使用在計時的應用)

- 提供待機模式(Halt mode)。

- 精準的+/- 0.5% 內阻震盪。

- 提供低壓復位(LVR=1.8V),看門狗計時(WDT),I/O復位功能(External Reset)。

# Nyquest 🕪

- 一個中斷輸入可連結到一組獨立的堆疊(Stack),並有多種中斷來源可以使用。

- 最多 20 根彈性的雙向 I/O,每根 I/O 功能皆可由單獨暫存器控制。

- IR紅外線輸出:提供31KHz~58KHz可選擇的紅外線頻率輸出,並可選擇高電平/低電平編碼。

- 多組 PWM-IO 分時多工,每通道 8-bit 解析度。

- 提供4通道的語音/Midi合成功能,可以單獨設定每個通道爲語音或Midi輸出。

- 更先進的高音質ADPCM語音合成演算法,可以經由簡單的調整採樣位數來提升音質。

- 新高音質合成演算法可混合 ADPCM 或 PCM, ADSR 段内建 256 階 Midi 包絡 (Envelope) 合成。

- 一組12-bit PWM純硬體輸出,可以直接驅動喇叭或蜂鳴片;一組12-bit DAC純硬體輸出,可以外加放大線路

來放大音量。

- 提供三階音量PWM輸出 (Normal/ Large/ Ultra),輸出語音不需外加電晶體放大。

- 内建16階硬體音量控制(Volume Control),用於進行整體音量的控制。

- 支援 Quick-IO 訊號控制。

- 內建低電壓偵測 (LVD) 可用來監控當前電壓狀態,避免電壓不穩定導致系統出錯。

- 提供特殊的快速燒錄模式,以加快OTP燒錄時間。

- 支援特殊的ICP (In Circuit Programming) 燒錄功能,以方便客戶先組裝PCBA模組再進行燒錄。

- 提供可程式的Code資料保護模式。(當Security-Bit 被燒斷後,資料將無法讀取。)

- 提供多種出貨型態,以滿足客戶不同的應用需求。

# **1. GENERAL DESCRIPTION**

The NY5Q series IC is a powerful 4-bit micro-controller based sound processor with embedded OTP (One Time Programmable) from New NY5 series (NY5+). There are 4 channels that are configured as speech or MIDI, and all of them can be auto-played back simultaneously. By using the high fidelity ADPCM speech synthesis algorithm, it can produce outstanding quality voices. Wide range sampling rate up to 44.1kHz and different volume level are supported. It is also equipped two kinds of audio outputs with fine resolution, including a current D/A converter and a PWM direct-drive. PWM mode also enhanced with noise-shaping function. The RISC MCU architecture is very easy to program and control, various applications can be easily implemented. There are 43 instructions, and most of them are executed in single cycle. Furthermore, in addition to the HALT mode (sleep mode), it offers the SLOW mode to minimize power dissipation.

# 2. FEATURES

- Wide operating voltage range: 2.0V to 5.5V.

- 4-bit RISC type micro-controller with 43 instructions.

- There are 10 OTP bodies. 832Kx10-bit ROM is the maximum. Program and voice data share the same ROM space. The voice duration, ROM size and I/O counts are shown below.

| ІС Туре  | Time* (sec) | ROM (bits) | RAM (bits) | I/O | PWM-IO | Channel | DAC |

|----------|-------------|------------|------------|-----|--------|---------|-----|

| NY5Q020A | 18.3        | 48K x 10   | 248 x 4    | 8   | -      | 4       | Y   |

| NY5Q026A | 25          | 64K x 10   | 248 x 4    | 4   | -      | 4       | Y   |

| NY5Q040A | 38.3        | 96K x 10   | 248 x 4    | 8   | -      | 4       | Y   |

| NY5Q046A | 45          | 112K x 10  | 248 x 4    | 12  | 8      | 4       | Y   |

| NY5Q060A | 58.3        | 144K x 10  | 248 x 4    | 16  | 8      | 4       | Y   |

| NY5Q080A | 78.3        | 192K x 10  | 248 x 4    | 12  | 8      | 4       | Y   |

| NY5Q092A | 91.6        | 224K x10   | 248 x 4    | 16  | 8      | 4       | Y   |

| NY5Q160A | 158.3       | 384K x 10  | 248 x 4    | 12  | 8      | 4       | Y   |

| NY5Q172A | 171.6       | 416K x 10  | 248 x 4    | 16  | 8      | 4       | Y   |

| NY5Q342A | 345         | 832K x 10  | 248 x 4    | 20  | 8      | 4       | Y   |

\* The voice duration is calculated at 6 KHz by 4-bit ADPCM algorithm.

- 248x4-bit RAM maximum, indirect RAM addressing mode is supported.

- 1MHz or 2MHz instruction frequency (2MHz is required for over 2-ch speech or MIDI).

- SLOW mode to operate at low power consumption.

- HALT mode to save power.

- Built-in RC oscillation is accurate with +/- 0.5% frequency deviation.

- Low voltage reset (LVR=1.8V), watch-dog reset and I/O port reset are all supported to protect the system.

# Nyquest 🕪

- Single interrupt entrance with an independent stack, multiple interrupt sources.

- Up to 20 flexible Bi-direction I/Os. Each I/O direction is independently controlled by individual register bit.

- Shared pins to provide IR carrier and external reset feature. (Mask option)

- Selection of IR carrier frequency and data high/low IR output is supported.

- Multiple groups of PWM-IO share a group of time, each channel has 8-bit resolution.

- NY5Q series are all 4 channels and can play simultaneously; each channel can be arbitrarily assigned as speech or MIDI channel based on the product spec.

- New high fidelity ADPCM speech synthesis algorithm.

- New high fidelity mixed ADPCM or PCM speech synthesis algorithm and ADSR with 256-step envelope for MIDI synthesis.

- High quality 12-bit D/A converter or 12-bit PWM driver.

- Support 3 levels Normal, Large, Ultra PWM current output.

- 16-level digital volume control for synthetic Speech/MIDI.

- Quick-IO control supported.

- Low Voltage Detector (LVD) is built-in for monitoring the status of power and protect malfunction if unstable power is given.

- A unique fast writing mode is provided to speed up OTP writing time.

- A special ICP (In Circuit Programming) writing function is supported for user to fabricate PCBA in advance.

- Programmable code protection is provided. (When the Security-Bit is burnt down, data can't be read.)

- Various shipping type for different application requirement.

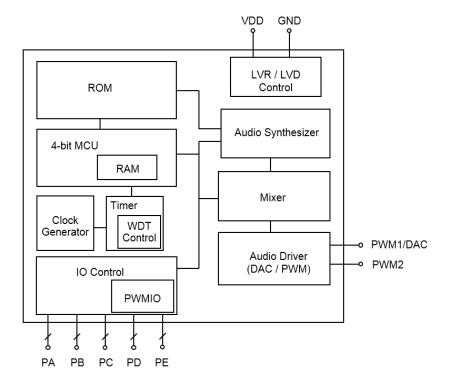

# 3. BLOCK DIAGRAM

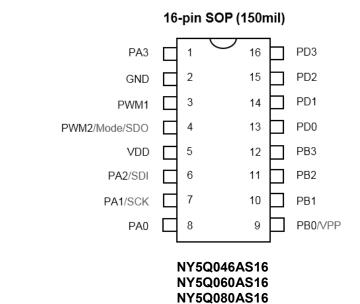

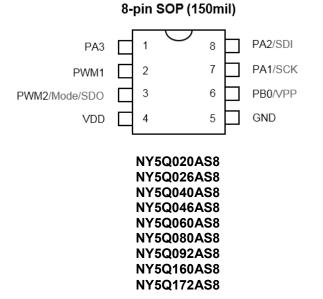

# 4. PAD DESCRIPTION

| Pin      | ATTR. | Description               |

|----------|-------|---------------------------|

| VDD#     | Power | Positive power            |

| GND#     | Power | Negative power            |

| PWM1/DAC | 0     | PWM1 output or DAC output |

| PWM2     | 0     | PWM2 output               |

| PA0~3    | I/O   | Bit 0~3 for Port A        |

| PB0~3    | I/O   | Bit 0~3 for Port B        |

| PC0~3    | I/O   | Bit 0~3 for Port C        |

| PD0~3    | I/O   | Bit 0~3 for Port D        |

| PE0~3    | I/O   | Bit 0~3 for Port E        |

\* (4 I/O) NY5Q026A : PB0, PA1, PA2, PA3

\* (8 I/O) NY5Q020A · NY5Q040A : PA0~3, PB0~3

\* (12 I/O) NY5Q046A < NY5Q080A < NY5Q160A : PA0~3, PB0~3, PD0~3

\* (16 I/O) NY5Q060A \ NY5Q092A \ NY5Q172A : PA0~3, PB0~3, PC0~3, PD0~3

\* (20 I/O) NY5Q342A : PA0~3, PB0~3, PC0~3, PD0~3, PE0~3

# Nyquest

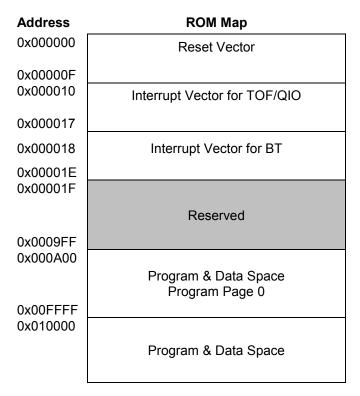

#### 5. MEMORY ORGANIZATION

There are maximum 832K words ROM, 248 nibbles of RAM and some dedicated system control register. The registers are divided into normal system registers and 8 nibbles of Multi-function registers.

#### 5.1 ROM

A large program/data/voice single ROM is provided, and its structure is shown below. The reserved region contains system information and can't be utilized by users. The program page is limited by the unconditional branch instruction: JMP and CALL. Because it can only handle 16-bit length address of ROM, the program page size is 64K words.

#### 5.2 RAM

NY5Q provide 248 nibbles RAM space. The address for RAM is 0x008~0x0FF. The first space from 0x08 to 0x3F is function RAM space, it only needs one-word instruction operation. And the second space from 0x040 to 0x0FF is data RAM space; the related operation is two-word instruction.

In addition to the immediate addressing mode, the indexed addressing mode is also supported. The page and address of the indexed RAM should be stored into RPT3 and RPT2 first, and users can read from or write in the XMD memory register to realize the indexed RAM access.

| Address        | RAM map                 |  |  |  |  |  |  |

|----------------|-------------------------|--|--|--|--|--|--|

| 0x000          |                         |  |  |  |  |  |  |

| 0,007          | Memory Register         |  |  |  |  |  |  |

| 0x007          |                         |  |  |  |  |  |  |

| 0x008          |                         |  |  |  |  |  |  |

| 0x03F          | 56 nibble Function RAM  |  |  |  |  |  |  |

| 0x03F<br>0x040 |                         |  |  |  |  |  |  |

| 0X040          |                         |  |  |  |  |  |  |

| 0x0FF          | 192 nibble Function RAM |  |  |  |  |  |  |

| 0x100          |                         |  |  |  |  |  |  |

| 0,1100         | Reserved                |  |  |  |  |  |  |

| 0x1C7          | The served              |  |  |  |  |  |  |

| 0x1C8          |                         |  |  |  |  |  |  |

|                | System registers        |  |  |  |  |  |  |

| 0x1CF          |                         |  |  |  |  |  |  |

| 0x1D0          |                         |  |  |  |  |  |  |

|                | Reserved                |  |  |  |  |  |  |

| 0x1DF          |                         |  |  |  |  |  |  |

| 0x1E0          |                         |  |  |  |  |  |  |

|                | System registers        |  |  |  |  |  |  |

| 0x1EF          |                         |  |  |  |  |  |  |

| 0x1F0          |                         |  |  |  |  |  |  |

| 0x1F3          | Reserved                |  |  |  |  |  |  |

| 0x1F3<br>0x1F4 |                         |  |  |  |  |  |  |

| UXIF4          | Queters excitates       |  |  |  |  |  |  |

| 0x1FF          | System registers        |  |  |  |  |  |  |

|                |                         |  |  |  |  |  |  |

# Nyquest

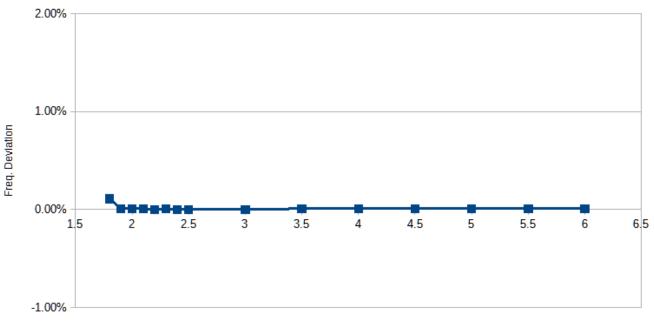

## 6. CLOCK GENERATOR

The clock generator is a Ring oscillator, and users can only select the internal resistor oscillation (INT-R). The INT-R oscillator accuracy is up to  $\pm 0.5\%$ .

# 7. INTERRUPT GENERATOR

There is one hardware interrupt and it has 3 different sources in NY5+. The interrupt event can be a fixed interval of the system base timer (BT), the timer overflow flag (TOF), or the quick-IO flag (QIOF). The TOF can be selected as one of the sample rate timer overflow by the register INT, and the QIOF arises as a QIO control code of any channel coming up. There is a system base timer in the NY5+ IC, which functions as long as the IC isn't in the halt mode. We provide 4 fixed intervals from the system base timer for interrupt source: 0.128, 0.256, 0.512 and 1.024ms.

As an interrupt occurs, NY5+ stores the accumulator (ACC), carry flag (C), zero flag (Z) and RAM page (PG) automatically. Then move PC to STK, and jump to the interrupt vector (0x000010 or 0x000018). An interrupt routine finishes with an IRET instruction. The IC draws the ACC, C, Z and PG back, and moves STK to PC back to jump back the main program.

The interrupt event of BT will be automatically cleared after entering the interrupt routine, but the TOF and QIOF have to be cleared by users.

### 8. IO PORTS

There are at most 20 I/O pins, designated as PAx through PEx, and x=0~3. All the I/O pins are bi-directional. An individual and independent register bit can determine the direction of each I/O pin. These register bits are PAIO (\$1E1), PBIO (\$1E3), PCIO (\$1E5), PDIO (\$1E7), and PEIO (\$1E9).

Using as input pin of each I/O, there are 3 kinds of mask option. Users can select input with pull-high resistor, input with register-controlled pull-high resistor (high-to-low wakeup only). If users want to enable/disable pull-high resistor by register during program execution, only high-to-low level change on this pin can wakeup NY5Q. On the other hand, if the pull-high resistor is fixed by option, either high-to-low or low-to-high level change on this pin can wakeup NY5Q. Users can refer user manual for details. The pull-high resistor of all the I/O pins has two kinds of option: weak and strong. The weak one is about  $1.2M\Omega@3V$  for normal application and the strong one is about  $100K\Omega@3V$  usually for key matrix function. When users decide this option, the same strength of pull-high resistor will be applied to all I/O pin.

Using as output pin of each I/O, there are 3 kinds of mask option. Users can select output with normal drive current and normal sink current or normal drive current and large sink current.

The PX0 port means the PA0, PB0, PC0, PD0, or PE0 port can also be optioned as an external reset pin or an infrared (IR) output pin. A reset port can possess a pull-high resister or not, and an IR port can be initial low or high and also large sink current or not.

### 9 LOW VOLTAGE DETECTOR (LVD)

There is one hardware voltage detector in NY5Q. It offers four levels for various application, 2.0v, 2.2v, 2.4v, 2.8v, 3.0v, 3.3v and 3.6v controlled by register \$LVD. The voltage detection function has to be enabled first, then select specific level for application, the flag will go to high while VDD is lower than selected level. User can check power status by setting different level and monitoring the flag.

#### **10. AUDIO SYNTHESIZER STRUCTURE**

There are 4-ch speech or MIDI audio output, and all modes are auto-played back by hardware. Different channel mode possesses different hardware structure. It provides a hardware mixer to mix the channel data. Two audio output stages: DAC and PWM are supported. Please noticed that 2MHz is required for over 2-ch speech or MIDI.

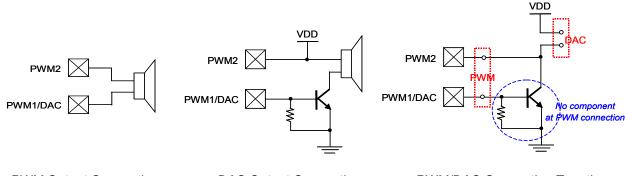

#### 10.1 Audio Output

By set the AUD register, PWM or DAC can be easily chosen as the audio output stage. Besides, it provides a pad detecting mechanism. The pad detecting mechanism detects the PWM2 pad during the reset initialization period, and sets the initial value of the audio output register as PWM if the PWM2 connection is floating, or sets the initial value of the audio output register as DAC if the PWM2 connection is high. In conclusion, connect the speaker to PWM1 and PWM2 only if using PWM, otherwise connect PWM2 to VDD if using DAC. Since the mechanism sets only the initial value of AUD, don't change the value of the AUD register if the pad detecting mechanism is adopted.

| PWM2 Pad           | Audio Output Initialization |

|--------------------|-----------------------------|

| Speaker (Floating) | PWM                         |

| VDD                | DAC                         |

PWM Output Connection

DAC Output Connection

PWM/DAC Connection Together

When using the PWM output, we provide an option of normal PWM current, large PWM current or ultra PWM current for different customer demand. The ultra PWM current consumes more current and makes sound louder.

#### **10.2 Volume Control**

Both PWM and DAC supports 16 steps hardware volume control by the VOL register, 0x0~0xF.

# 11 WATCH-DOG TIMER (WDT)

To recover from program malfunction, the NY5+ IC supports an embedded watch-dog timer reset. The WDTR function always works with the program executing. Users have clear the WDT periodically to prevent from timing up with a reset generation. Typically, the minimum time-up period of the WDT is about 15ms. Users can move a 0x5 value to the 0x1CA BTF system register to clear WDT.

# 12. Power Saving Mode

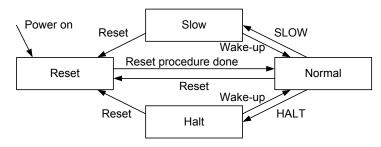

Power Saving Mode Flow Chart

#### 12.1 Halt Mode

The system enters the halt mode if the HALT command executed. The halt mode is also known as the sleep mode. As implied by the name, the IC falls asleep and the system clock is completely turned off, so all the IC functions are halted and it minimizes the power consumption.

The only way to wake-up the sleeping system is an input port wake-up. The IC keeps monitoring the input pads during the halt mode. If the input status of any input pad differs from the corresponding port register, the system will be waked-up. Then the succeeding instructions after the HALT instruction will be executed after the wake-up stable time (about 48us). So before executing the HALT instruction, users have to keep in mind to store the current input port statuses into port registers.

If the IC is waked-up from the halt mode by a reset port, it goes into the reset procedure.

#### 12.2 Slow Mode

The system enters the slow mode if the SLOW command executed. The system clock in the slow mode slows down about 32 times slower than in the normal mode. The difference between the halt mode and the slow is only the system clock. So the IC can be waked-up from the slow mode by the interrupt in addition to the input port. Since the sample rate timer and the audio engine are suspended during the slow mode, interrupt from TOF and QIOF in the slow mode can't operate, of course can't wake-up the system.

The input wake-up manner is the same as the halt mode. So before executing the SLOW instruction, users have to keep in mind to store the current input port statuses into port registers. If the IC is waked-up from the slow mode by a reset port, it goes into the reset procedure. After the IC is waked-up by the input port or an INT of BT, the succeeding instructions after the SLOW instruction will be executed after the wake-up stable time (128us maximum).

Remember to turn off the audio output before entering to the slow mode.

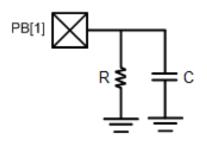

#### 12.3 RC Slow Mode

Another power saving mode is RC Slow mode, using external components with PB[1] and HALT commands, an application example is shown below.

There are three differences between using RC slow mode and slow mode. The first is that the user can adjust the value of R and C to determine the wake-up interval, instead of using the fixed BT interrupt. The second is that under the same interval time, the value of R can be increased, which saves more power during work. Third, the interval time of slow mode between different ICs will be slightly different and cannot be corrected. In RC slow mode, all products can get closer results by adjusting the value of RC. And it should be noted that the RC slow mode requires a resistor and a capacitor for charging and discharging, and the charging and discharging time will vary slightly with the voltage.

# **13. ELECTRICAL CHARACTERISTICS**

# 13.1 Absolute Maximum Rating

| Symbol    | Parameter             | Rated Value        | Unit |

|-----------|-----------------------|--------------------|------|

| Vdd - Vss | Supply voltage        | -0.5 ~ +6.0        | V    |

| Vin       | Input voltage         | Vss-0.3V ~ Vdd+0.3 | V    |

| Тор       | Operating Temperature | -20 ~ +70 (*)      | °C   |

| Tst       | Storage Temperature   | -40 ~ +125 (**)    | °C   |

(\*) Please make sure all other components can meet temperature range.

(\*\*) SOP package only.

# **13.2 DC Characteristics**

| Symbol          | Para                             | meter        | VDD      | Min. | Тур.       | Max. | Unit | Condition               |  |

|-----------------|----------------------------------|--------------|----------|------|------------|------|------|-------------------------|--|

| Vdd             | Operatin                         | g voltage    |          | 2.0  | 3          | 5.5  | V    | 2MHz                    |  |

| lsв             |                                  | Halt<br>mode | 3<br>4.5 |      | 1.2<br>1.5 |      | uA   | Sleep, no load          |  |

| I <sub>SL</sub> | Supply                           | Slow         | 3        |      | 30         |      | uA   | BT=1ms, no load         |  |

| ISL             | current                          | mode         | 4.5      |      | 35         |      | uA   | D1 – 1113, 110 10au     |  |

|                 |                                  |              | 3        |      | 0.8        |      | mA   | 1MHz, no loading        |  |

| lop             |                                  | Operating    | 4.5      |      | 0.9        |      |      | Tivil 12, 110 loading   |  |

| юр              |                                  | mode         | 3        |      | 1          |      | mA   | 2MHz, no loading        |  |

|                 |                                  |              | 4.5      |      | 1.1        |      | IIIA | Zivil 12, 110 loadility |  |

|                 |                                  | Weak         | 3        |      | 2.5        |      | uA   |                         |  |

| II.             | Input current<br>(Internal pull- | (1.2M ohms)  | 4.5      |      | 6          |      | uA   | V <sub>IL</sub> =0V     |  |

| ΠL              | high)                            | Strong       | 3        |      | 30         |      | uA   | VIL-OV                  |  |

|                 | <b>U</b>                         | (100K ohms)  | 4.5      |      | 70         |      | uA   |                         |  |

| Іон             | Output bi                        | gh current   | 3        |      | -7         |      | mA   | V <sub>OH</sub> =2.0V   |  |

| ЮН              | Output III                       | gricultent   | 4.5      |      | -11        |      | IIIA | V <sub>ОН</sub> =3.5V   |  |

|                 |                                  | w current    | 3        |      | 11         |      | mA   |                         |  |

|                 | (Normal                          | current)     | 4.5      |      | 19         |      | mA   | <u>)</u> ∕ −1 0)/       |  |

| IOL             | Output lo                        | w current    | 3        |      | 23         |      | mA   | V <sub>OL</sub> =1.0V   |  |

|                 | (Large                           | current)     | 4.5      |      | 36         |      | mA   |                         |  |

|                 |                                  | out current  | 3        |      | 60         |      | mA   |                         |  |

|                 | (Noi                             | rmal)        | 4.5      |      | 100        |      | IIIA |                         |  |

| РWM             | PWM out                          | out current  | 3        |      | 70         |      | mA   | Load=8 ohms             |  |

|                 | (La                              | rge)         | 4.5      |      | 117        |      | IIIA |                         |  |

|                 |                                  | out current  | 3        |      | 80         |      | mA   |                         |  |

|                 | (UI                              | tra)         | 4.5      |      | 125        |      |      |                         |  |

| Idac            | DAC out                          | out current  | 3        |      | 1.4        |      | mA   | Half scale              |  |

|                 |                                  |              | 4.5      |      | 1.6        |      |      |                         |  |

# NY5QxxxA Series

| Symbol | Parameter               | VDD | Min. | Тур. | Max. | Unit | Condition                                  |

|--------|-------------------------|-----|------|------|------|------|--------------------------------------------|

| ∆F/F   | Frequency deviation     | 3   |      | -0.5 |      | %    | Fosc(3.0v)-Fosc(2.4v)<br>Fosc(3v)          |

|        | by voltage drop         | 4.5 |      | 0.5  |      | 70   | <u>Fosc(4.5v)-Fosc(3.0v)</u><br>Fosc(4.5v) |

| ∆F/F   | Frequency lot deviation | 3   | -0.5 |      | 0.5  | %    | <u>Fmax(3.0v)-Fmin(3.0v)</u><br>Fmax(3.0v) |

| Газа   | Ossillation Frequency   | -   | 0.95 | 1    | 1.05 | MHz  | 1MHz, VDD=2.0~5.5V                         |

| Fosc   | Oscillation Frequency   | -   | 1.90 | 2    | 2.10 | MHz  | 2MHz, VDD=2.0~5.5V                         |

# 13.3 Voltage vs. Frequency

Voltage vs Freq. Deviation (6.0K Hz@3.0v)

Voltage(V)

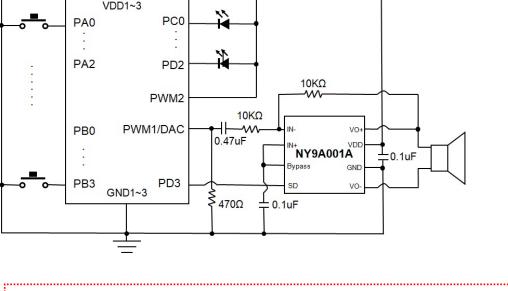

### **14. APPLICATION**

#### (1) PWM Direct-Drive

C1 C1 VDD1~3 VDD1~3 K PC0 PC0 PA0 PA0 PD3 PD3 PA3 PA3 PB0 PB0 PWM2 PWM2 PWM1/DAC PB3 PB3 PWM1/DAC 8050 ş GND1~3 GND1~3 Rbias C1 VDD1~3

(2) DAC Output with BJT

(3)DAC Output with Amplifier

Note: C1 is VDD power cap and cannot be omitted. C1 must be placed near to NY5Q Chip. Cap value should be at least 0.22uF if VDD is over 4.5V or choosing PWM sound "High Quality" option.

Note: PB0 is VPP pin for writer. Please avoid motor, relay, or any inductor application to make higher voltage than VDD.

## **15. DIE PAD DIAGRAM**

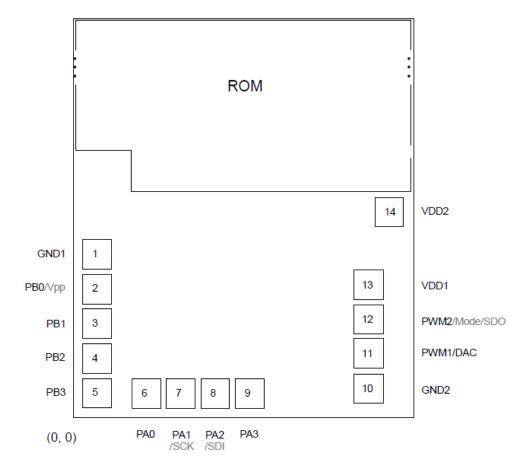

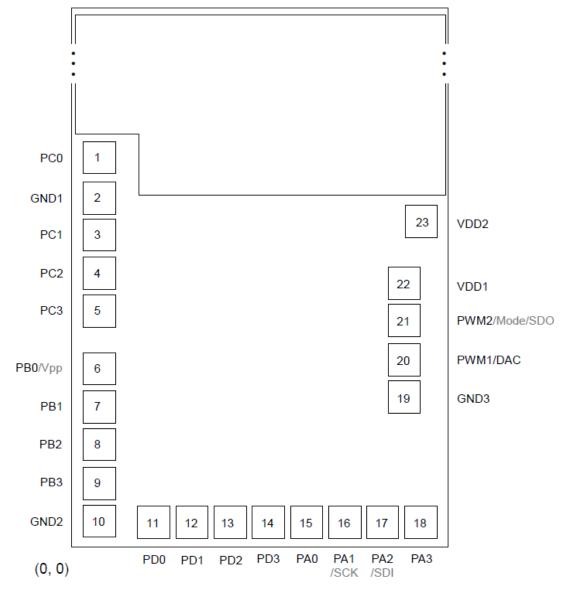

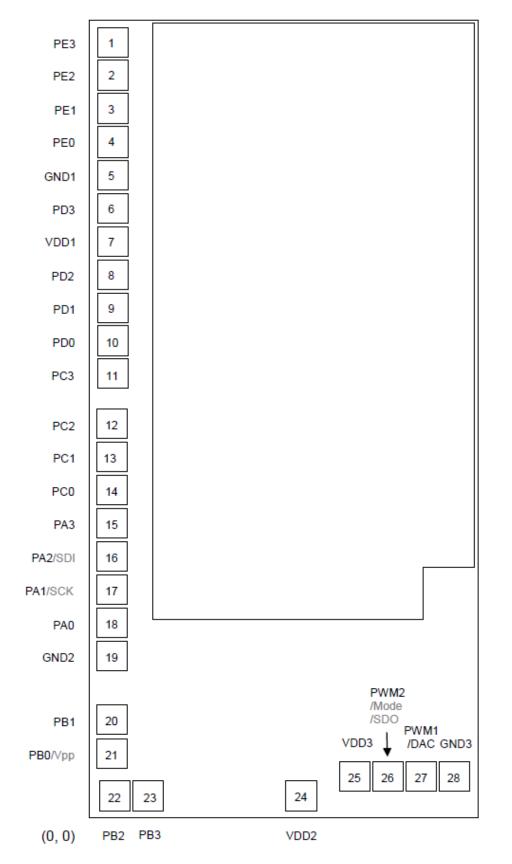

#### 15.1 NY5Q020A / NY5Q040A

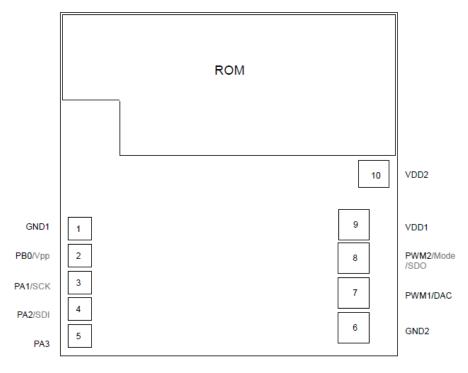

#### 15.2 NY5Q026A

#### 15.3 NY5Q060A / NY5Q092A

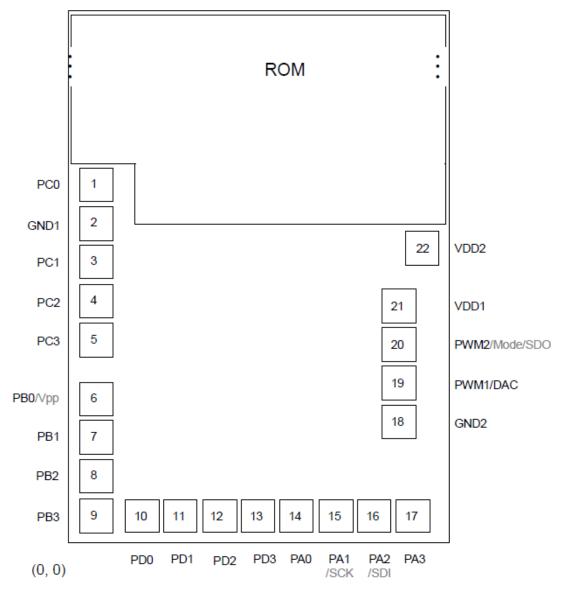

#### 15.4 NY5A046A / NY5Q080A / NY5Q160A

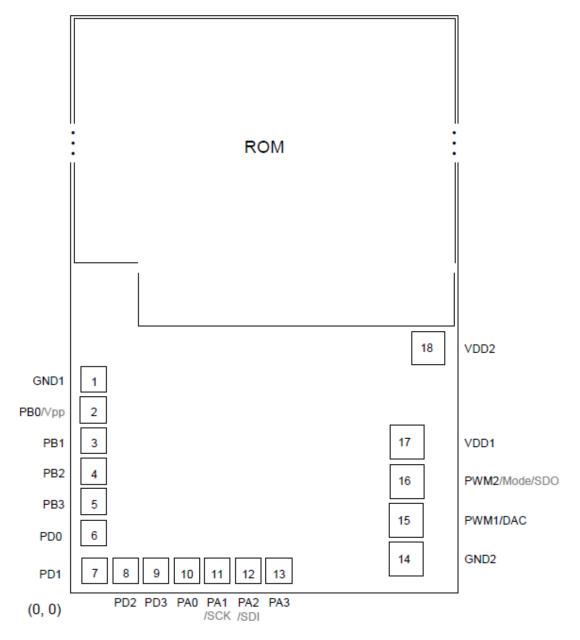

#### 15.5 NY5Q172A

#### 15.6 NY5Q342A

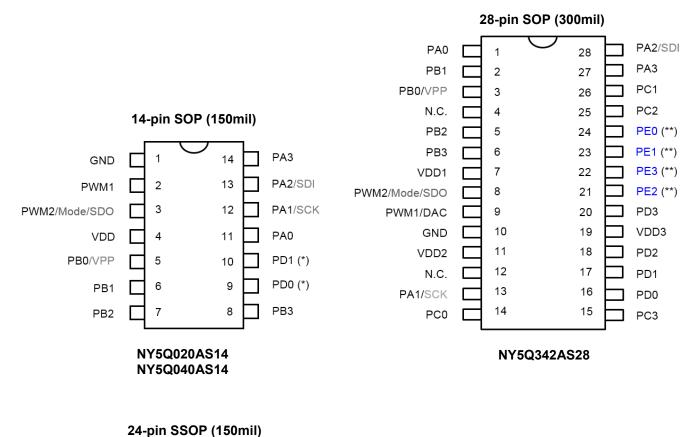

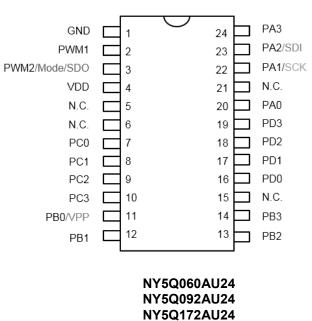

# **16. PACKAGE PIN ASSIGNMENT**

- \* Pin 9, 10 for SOP14 is reserved for PD0, PD1. Those pins are N.C. for NY5Q020A, NY5Q040A

- \*\* NY5Q342AS28 is compatible with NY5P345JS28 and NY5P185BS28 except PE0~3.

# NY5QxxxA Series

NY5Q092AS16 NY5Q160AS16 NY5Q172AS16

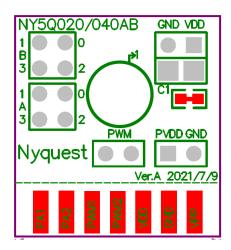

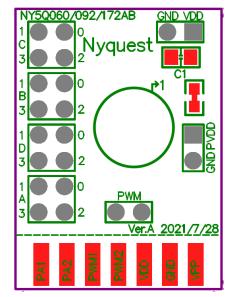

# **17 COB PIN ASSIGNMENT**

NY5Q020AB, NY5Q040AB (8 I/O)

NY5Q060AB, NY5Q092AB, NY5Q172AB (16 I/O)

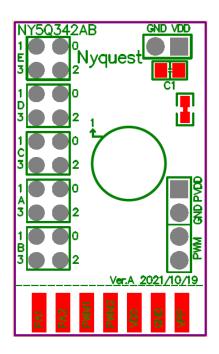

#### NY5Q342AB (20 I/O)

## **18. PACKAGE DIMENSION**

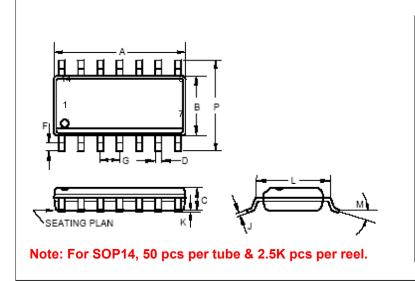

### 18.1 14-Pin Plastic SOP (150 mil)

|   | I     | NCHES   | 5     | MILLIMETERS |      |      |  |

|---|-------|---------|-------|-------------|------|------|--|

|   | MIN   | TYP     | MAX   | MIN         | TYP  | MAX  |  |

| А | 0.337 | -       | 0.344 | 8.55        | -    | 8.75 |  |

| В | 0.144 | -       | 0.163 | 3.66        | -    | 4.14 |  |

| С | 0.049 | -       | 0.063 | 1.25        | 1    | 1.60 |  |

| D | 0.012 | -       | 0.020 | 0.30        | I    | 0.51 |  |

| F | 0.012 | -       | 0.044 | 0.30        | I    | 1.12 |  |

| G | 0.    | .050 BS | С     | 1.27 BSC    |      |      |  |

| J | -     | 0.008   |       | -           | 0.20 | -    |  |

| к | 0.002 | -       | 0.010 | 0.05        | -    | 0.25 |  |

| L | 0.189 | -       | 0.205 | 4.80        | -    | 5.21 |  |

| М | -     | -       | 8°    | -           | -    | 8°   |  |

| Ρ | 0.224 | -       | 0.248 | 5.70        | -    | 6.30 |  |

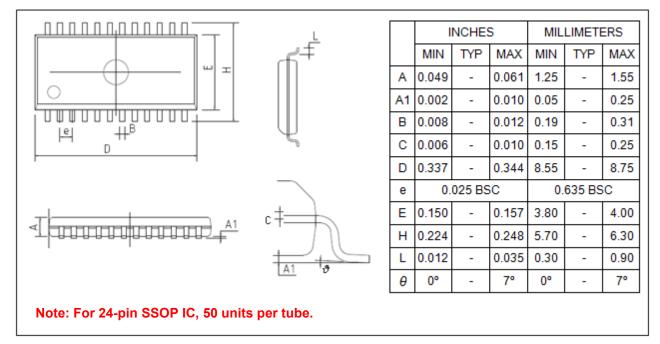

#### 18.2 SSOP-24 (150mil, 0.635mm pin pitch)

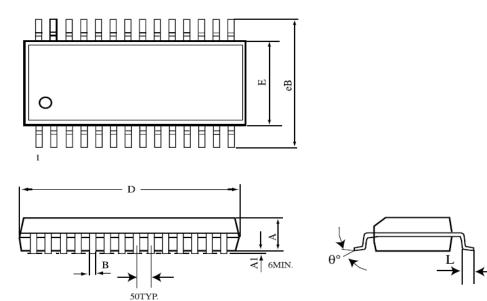

# 18.3 28-Pin Plastic SOP (300 mil)

| Sym.             | Dimen | sion in mi | ls   | Dime   | nsion in m | m      |

|------------------|-------|------------|------|--------|------------|--------|

|                  | Min.  | Nom.       | Max. | Min.   | Nom.       | Max.   |

| А                | 90    | 92         | 94   | 2.286  | 2.337      | 2.388  |

| A1               | 6     |            |      | 0.152  |            |        |

| В                | 12    | 16         | 20   | 0.305  | 0.406      | 0.508  |

| D                | 703   | 705        | 707  | 17.856 | 17.907     | 17.958 |

| Е                | 293   | 295        | 297  | 7.442  | 7.493      | 7.544  |

| eB               | 406   | 410        | 414  | 10.312 | 10.414     | 10.516 |

| L                | 25    |            |      | 0.635  |            |        |

| $\theta^{\circ}$ | 0°    | 4°         | 8°   | 0°     | 4°         | 8°     |